Binäre Multiplikation

Um die Multiplikation von Binärzahlen zu verstehen ist es nötig, sich die schriftliche Multiplikation ins Gedächnis zu rufen. Hierbei multipliziert man die

erste Ziffer der zweiten Zahl mit der gesamten ersten Zahl, dann die zweite Ziffer der zweiten Zahl mit der gesamten ersten Zahl etc.

Die Ergebnisse schreibt man immer eine Stelle versetzt untereinander, wie in Abbildung 1 dargestellt.

13•12

13

+ 26

156

Abbildung 1: Schriftliche Multiplikation

von Dezimalzahlen

Die Multiplikation von Binärzahlen funktioniert auf die selbe Weise. Da es hier allerdings nur die Ziffern 0 und 1 gibt ist es deutlich einfacher

die jeweiligen Ziffern der zweiten Zahl mit der ersten Zahl zu multiplizieren.

Entweder ist die Ziffer eine 1, so wird die ganze erste Zahl hingeschrieben oder es ist eine 0, so ist das Ergebnis auch eine 0.

Das Beispiel aus Abbildung 1, wo 13•12 gerechnet wird, ist in Abblidung 2 binär dargestellt (13=1101b und 12=1100b).

1101•1100

1101

+ 1101

+ 0000

+ 0000

10011100 (=156)

|

Abbildung 2: Multiplikation

von Binärzahlen

Multiplizierwerk

Allgemein kann man für die binäre Multiplikation somit sagen, dass immer ein Bit der zweiten Zahl mit der ersten Zahl mit Und verknüpft wird.

Denn ist das Bit 0 ergibt jedes Und eine 0 und ist dieses Bit eine 1, so ergibt es wieder die erste Zahl.

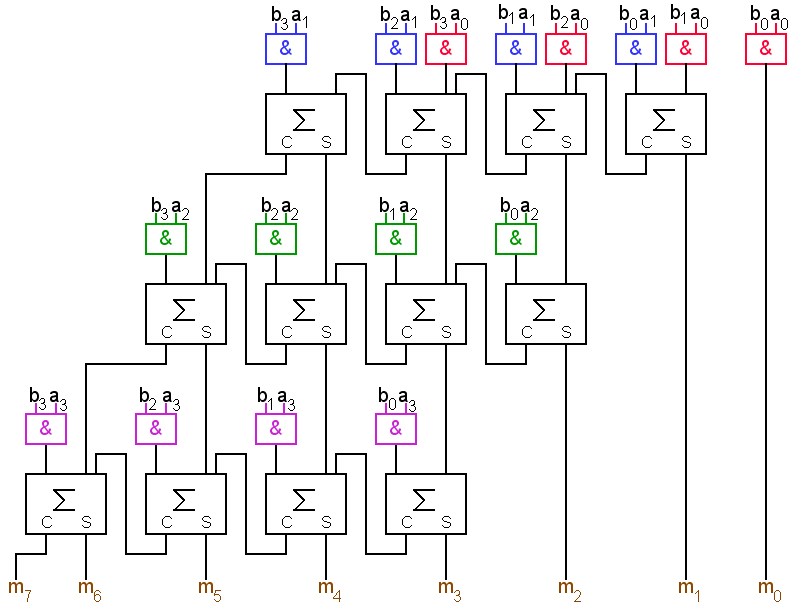

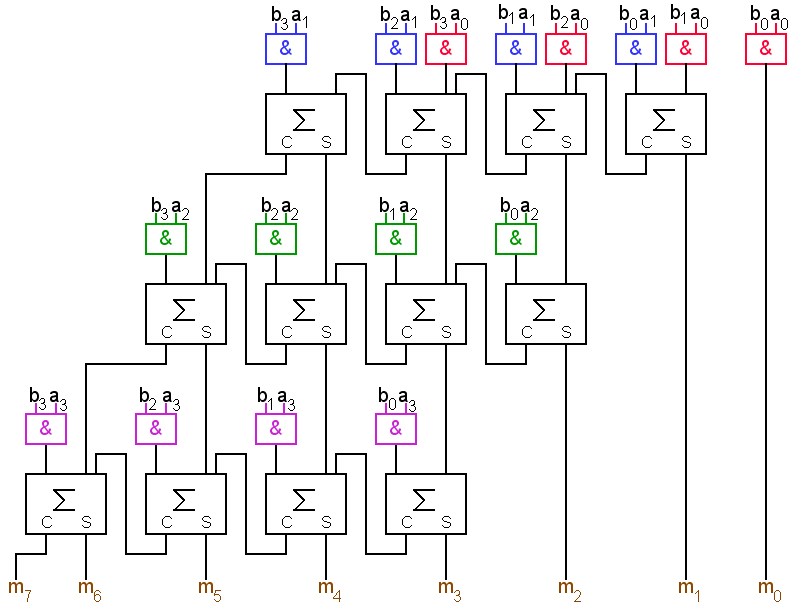

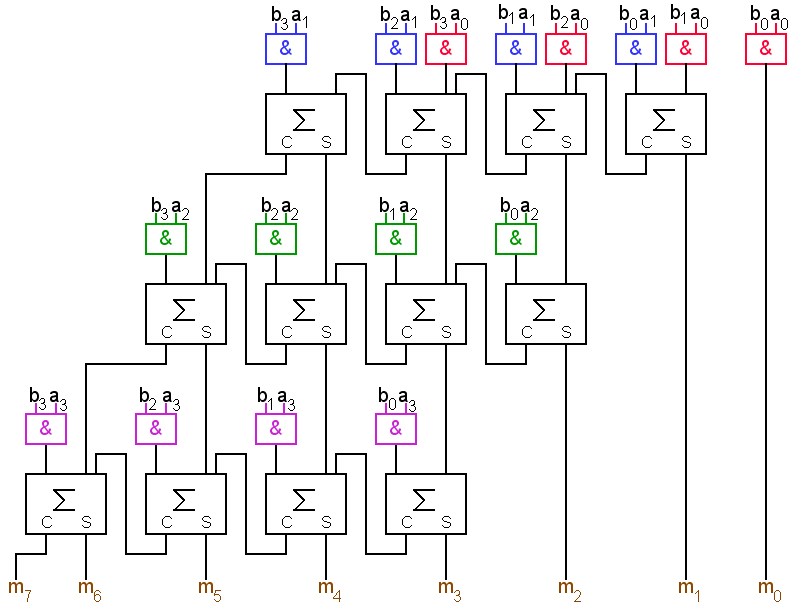

Werden die Zahlen, welche sich durch die Und-Verknüpfungen ergeben stellenrichtig untereinander geschrieben erhält man das in

Abbildung 3 dargestellte Ergebnis.

Die Ziffern m0 bis m7 stellen das Ergebnis dar, wobei m7 den letzten Übertrag darstellt.

|

b3b2b1b0• |

a3 |

a2 |

a1 |

a0 |

| | | b3∧a3 | b2∧a3 | b1∧a3 | b0∧a3 | | | |

| + | | | b3∧a2 | b2∧a2 | b1∧a2 | b0∧a2 | | |

| + | | | | b3∧a1 | b2∧a1 | b1∧a1 | b0∧a1 | |

| + | | | | | b3∧a0 | b2∧a0 | b1∧a0 | b0∧a0 |

| = |

m7 |

m6 |

m5 |

m4 |

m3 |

m2 |

m1 |

m0 |

Abbildung 3: allgemeine binäre Multiplikation

zweier 4-Bit Zahlen |

Die in Abbildung 3 dargestellte Multiplikation wird eins zu eins in ein Schaltnetz umgewandelt.

Hierzu werden, wie in Abbildung 3 ersichtlich 16 Und-Gatter benötigt. Zusätzlich werden bei einer 4-Bit-Multiplikation drei Additionen druchgeführt.

Hierfür kommen 3 mal 4 Addierer zum Einsatz.

Die Teilergebnisse in Abbildung 3 und Abbildung 4 sind zur Übersichtlichkeit gleich eingefärbt.

Abb 4: 4-Bit Multiplizierer

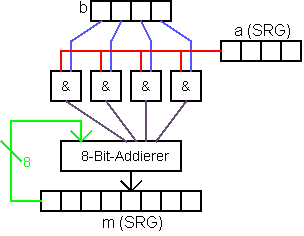

Serielles Multiplizierwerk

In vielen ALUs werden serielle Multiplizierwerke verwendet. Dies hat den Hintergrund, dass ein Multiplizierwerk wie in Abbildung 4 dargestellt eine

Durchlaufzeit von mehreren Takten hat. Das "überspringen" von Takten erschwert jedoch den Entwurf des Steuerwerks.

Bei einem seriellen Addierer wird mit jedem Takt ein Teil der Multiplikation berechnet.

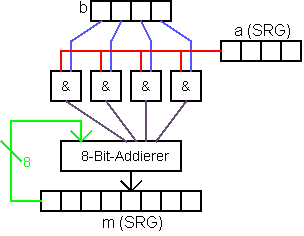

In Abbildung 5 ist ein Serieller Multiplizierer schematisch dargestellt. Die Register a und m sind hier Schieberegister.

Beide werden bei einem Takt nach links geschoben. Das Register b ist fest (also keine Schieberegister).

Somit erhält man vor dem ersten Takt a3&(b) in m. Danach wird a und m um eine Stelle weitergeschoben und a2&(b) hinzuaddiert.

Somit erhält man Schritt für Schritt die in Abbildung 3 dargestelle Rechnung.

Abb 5: 4-Bit Multiplizierer